### Early Robustness Validation of Automotive FlexRay Topologies through a Simulation-Based Method

Thorsten Gerke Technical Marketing Europe Synopsys GmbH

## **Overview**

- Introduction & Motivation

- Robust Design Method & Models

- Critical Points of FlexRay's EPL

- Application Example

- Summary

# Introduction

### **FlexRay Protocol**

- New In-Vehicle Networking standard

- Developed for safety-relevant applications like xby-wire and control systems

- Time triggered communication cycle (real time condition)

- High-speed transmission rate (10 MBit/s)

- Fault tolerant behavior (Dual channel)

# Introduction

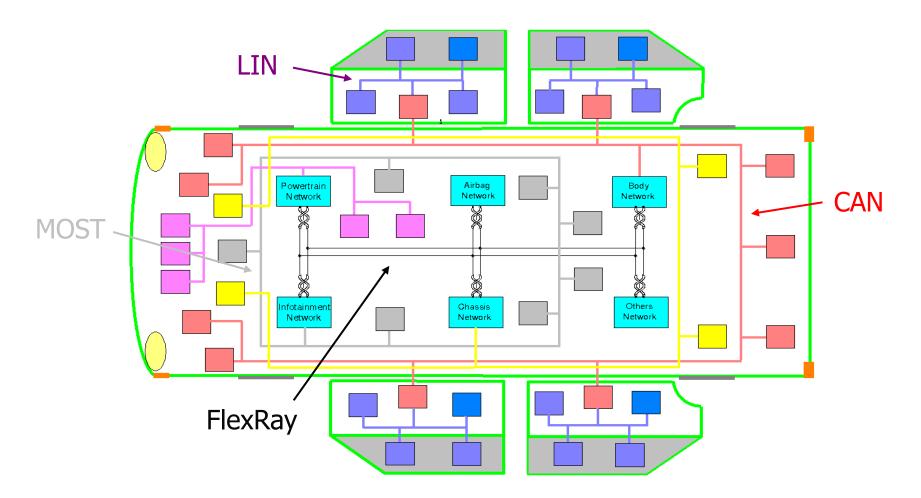

### **Future In-Vehicle Network Architecture**

## **Basics**

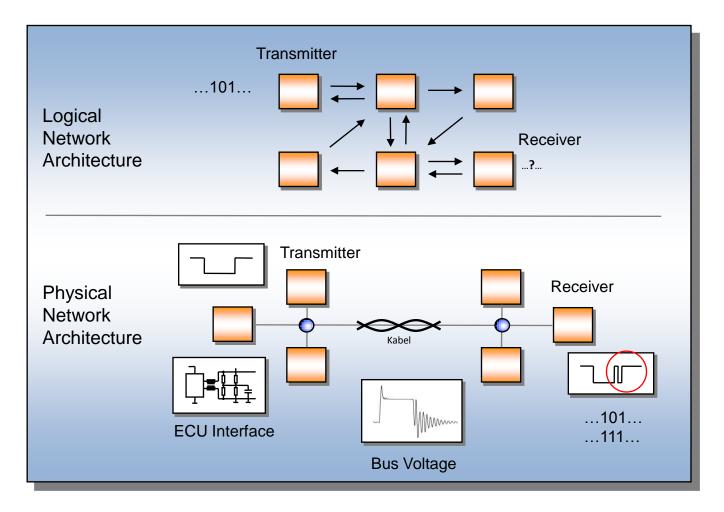

### **Logical vs. Physical Network Architecture**

# **Motivation**

### FlexRay EPL Topology Challenges

- Topology guidelines

- FlexRay's EPL specification provides rough guidelines

- EPL spec kept flexible for system optimization

- Analysis of EPL criteria requires the validation of the specific topology

- Different architecture compromises

- Active/Passive star

- Linear bus

- Central/decentral termination

- Impact on signal integrity no longer predictable

# Motivation

### FlexRay EPL Topology Challenges (2)

- Variants

- Number of ECUs depends on vehicle equipment

- Not all variants are available before Start Of Production (SOP)

- Changes

- Cost intensive

- Time consuming (critical when close to SOP)

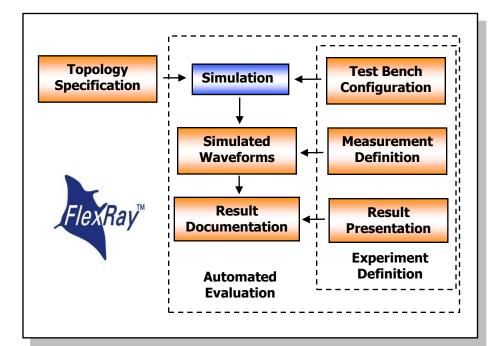

- Simulation is the only choice to sufficiently evaluate topologies in the early development phase

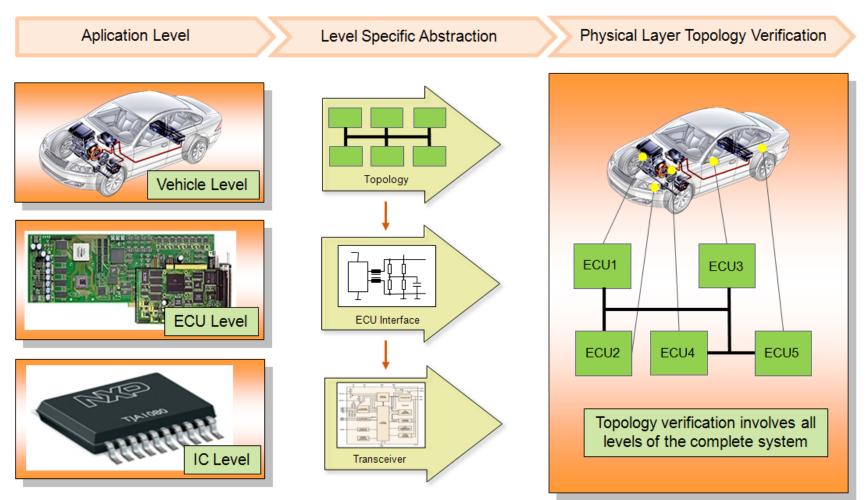

### **Basics** FlexRay Topology Verification

### **Basics** Overall Goal – FlexRay Physical Layer

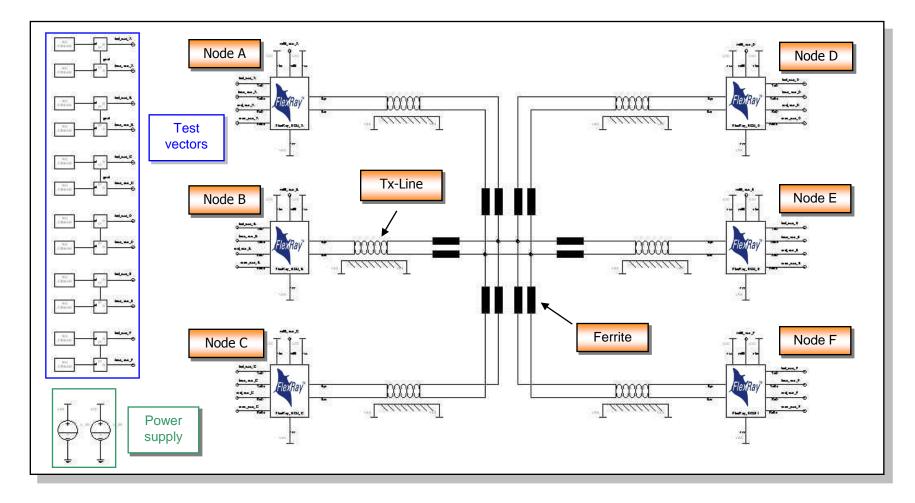

**Simulation Environment & Models**

- FlexRay network simulated in Saber

- Required simulation models

- ECU

- Bus interface (analog)

- Transceiver

- Common mode choke

- Transmission line

- Ferrites

- Models based on MAST Hardware Description Language (HDL)

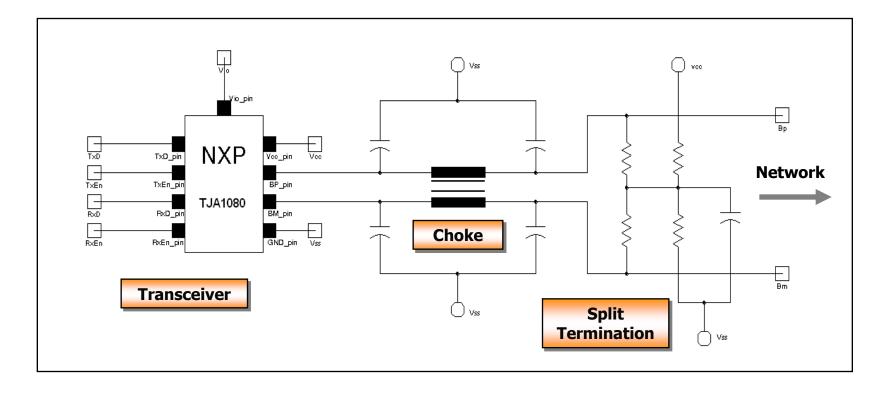

### Simulation ECU Interface Model

**FlexRay Transceiver Model**

- TJA1080 FlexRay transceiver

- Developed by IC manufacturer (NXP Semiconductor)

- Behavioral model according to data sheet

- Mode transitions

- Analog behavior at connection pins

- Transmitter and receiver asymmetries

- Support of worst case behavior

- Specially developed for system simulation

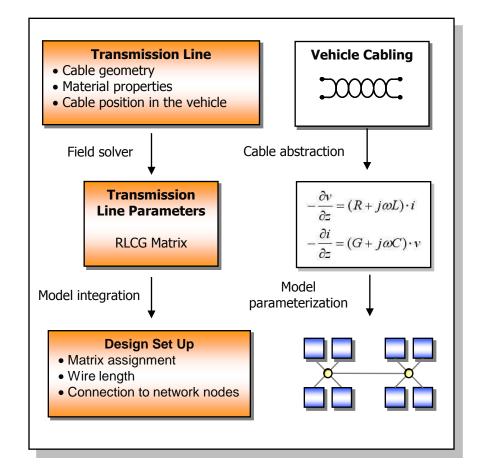

### **Transmission Line Model**

- Developed based on spec from FlexRay EPL working group

- Equations defined in frequency domain

- Wire length as model argument

- Skin Effect

- Support of both differential and common mode

- Validated by measurements

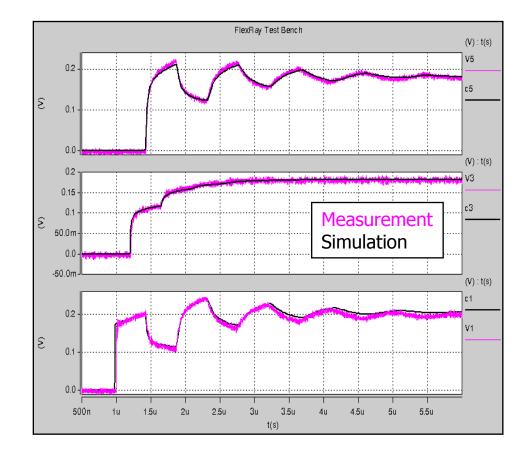

**TxLine – Simulation vs. Measurement**

- Validation test benches defined by FlexRay EPL working group

- 96m cable length

- High/Low impedance terminated branches

- Unterminated branches

- Perfect matching between simulation results and measurements

## Critical Points of FlexRay's EPL Validation Criteria

- Critical aspects of the signal integrity of a FlexRay<sup>™</sup> network

- Signal propagation delay

- Asymmetric delay

- Bit deformation due to ringing and reflections

- Truncation of transmission start sequence (Transition idle to active)

- Frame Stretching due to ringing after last bit (Transition active to idle)

## Critical Points of FlexRay's EPL Propagation Delay

- Propagation delay → Synchronization precision relevant

- Time lapse between the falling edges of transmitter and receiver nodes in the network

- Depends mainly on the topology of the path

- Bus load

- Temperature

- Supply voltage variations

- $\rightarrow$  Simulation is the only choice for investigation!

- The FlexRay protocol defines a constraint for the propagation delay between two nodes n and m

### $dPropagationDelayM, N \leq cPropagationDelayMax$

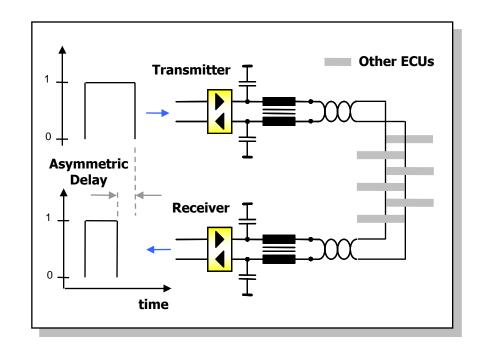

# Critical Points of FlexRay's EPL

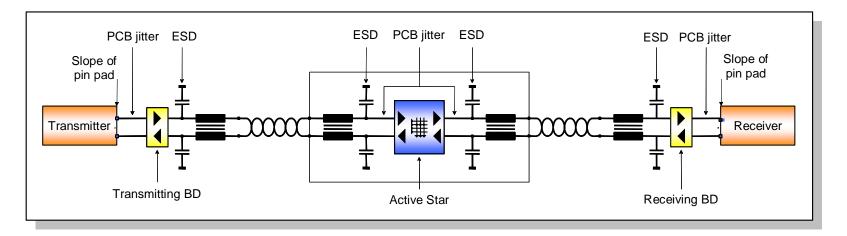

### Asymmetry

- Relevant for correct signal decoding

- Mismatching between negative and positive edge propagation delays of the bus drivers and active stars

- Non-symmetric split termination networks

- Non-balanced ESD protection elements

- The greater the total asymmetry of the topology path the lower the robustness against injection of EM fields

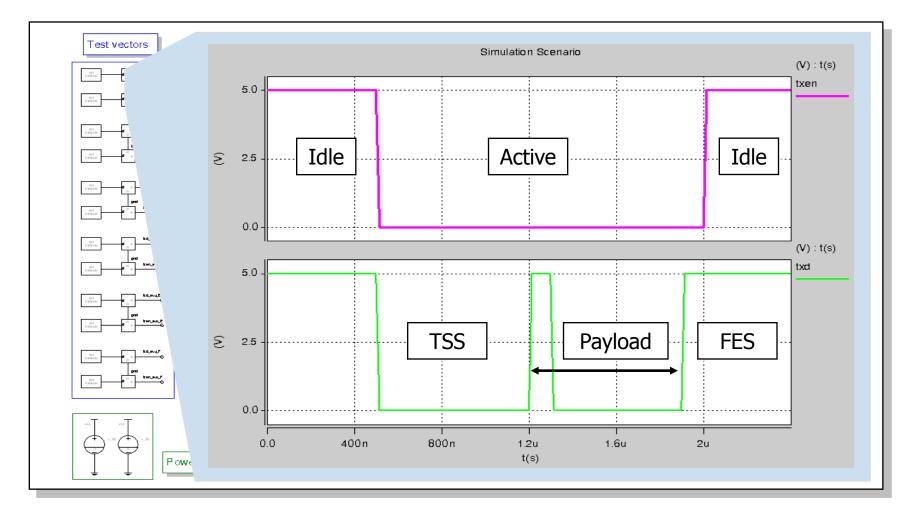

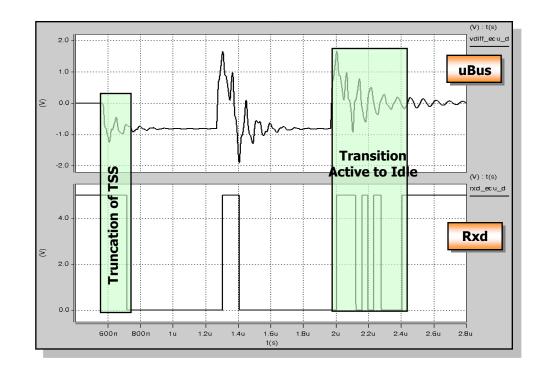

### Critical Points of FlexRay's EPL Truncation of TSS

- Each communication element starts with the so called <u>Transmission Start Sequence</u> (TSS)

- Relevant for the transition from bus idle to bus active

- During the transition from bus idle to active the sequence of data can be shortened

- Activity detection in the receiver BDs and Active stars

- Filter time for activity detection plus internal logic

- Sufficient TSS length depends on the topology

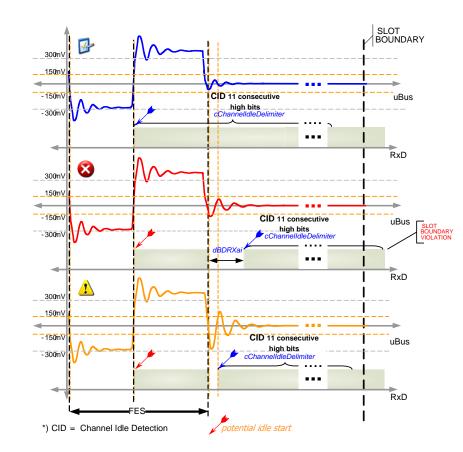

## Critical Points of FlexRay's EPL Transition Active to Idle

- Frame stretching due to ringing after last frame bit

- The <u>channel idle recognition</u> <u>point</u> (CHIRP) is shifted

- Critical problem especially

beyond cascaded active stars

- A static slot may be corrupted, boundary violation may appear

- The scenario may lead to an error in dynamic segment

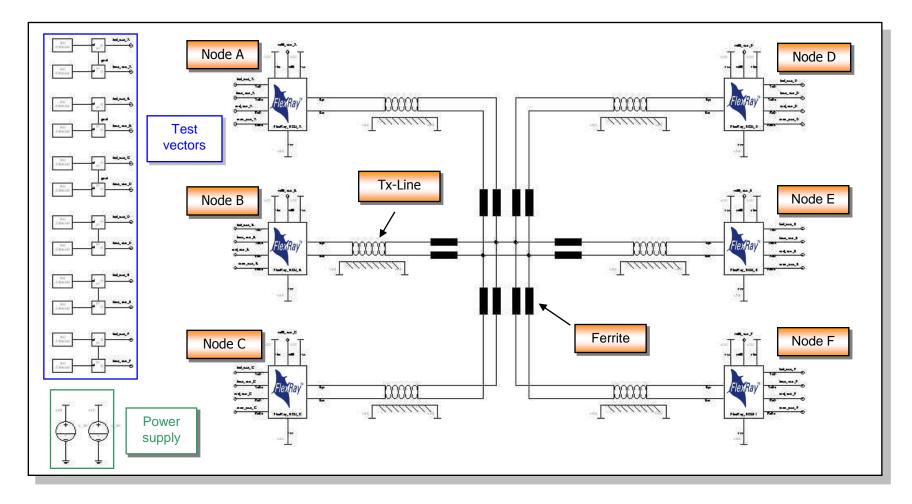

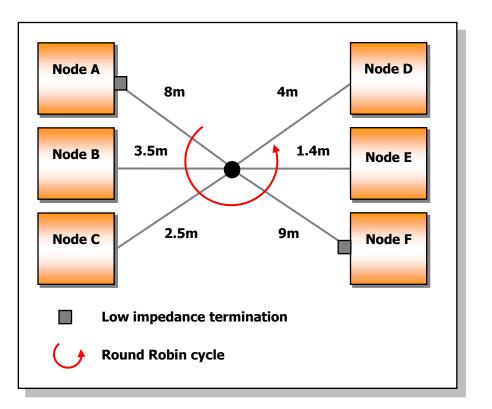

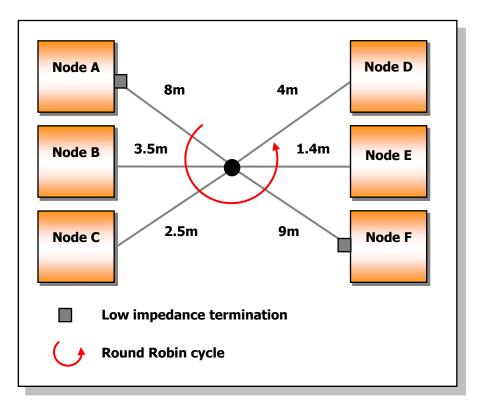

### **Application Example** Round-Robin Communication

- Six ECU nodes

- Passive star architecture

- Round-Robin communication

- Low impedance split termination → nodes with the largest distance

- Ferrites as passive filter elements in the center of the star

### **Application Example** First Scenario - Test Bench

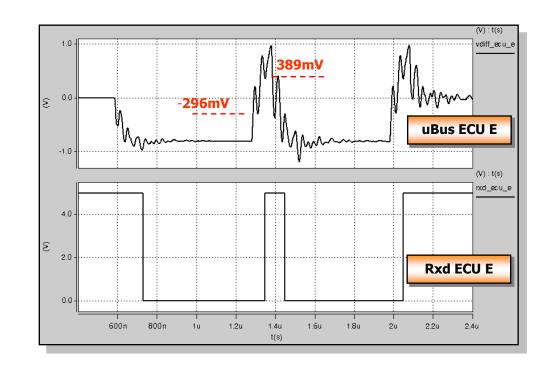

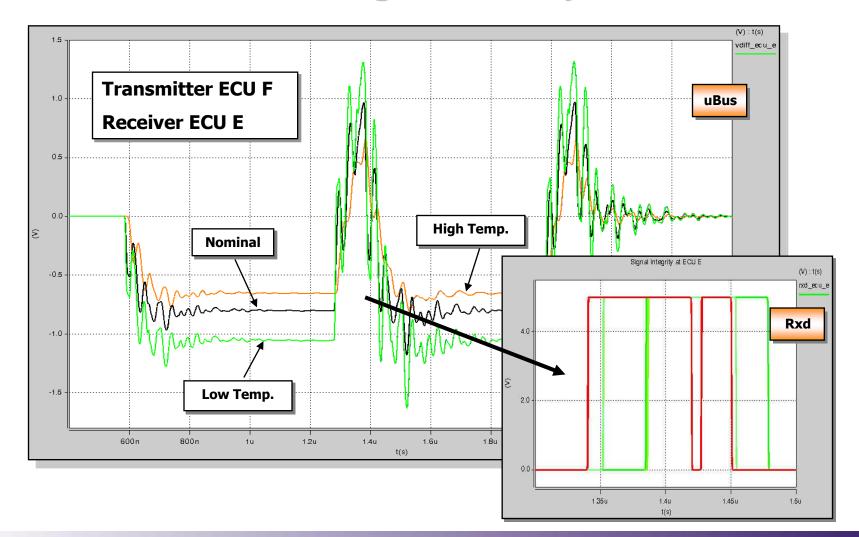

## **Application Example** First Scenario - Signal Quality

- Voltage peaks magnitudes in the range of -296mV and 389mV

- Transceiver nominal input threshold (±225mV)

- Peaks are filtered through low pass filter

- Considering worst case threshold (±150mV) this may result in multiple switching of the Rxd signal

## Application Example First Scenario - Ringing → Active to Idle

- Repeated switching on the digital RxD pin

- The potential idle start event is delayed significantly, in this case 0.4 us

- The channel idle recognition point (CHIRP) is shifted

The maximum allowable duration of this effect will be prescribed in the physical layer specification.

## **Application Example** First Scenario - Asymmetric Delays

- Limits for asymmetric delays defined in FlexRay EPL Spec

- Need to be evaluated for complete Round Robin communication and each ECU

- Manual evaluation could be very time consuming

- Automated approach is used to generate Matrix written in Excel

### **Application Example** Asymmetric Delays – Automation

#### **One button solution**

| M         | licrosoft Exce    | el - Book               | 1                    |                  |                           |                      |                       | _              |         |

|-----------|-------------------|-------------------------|----------------------|------------------|---------------------------|----------------------|-----------------------|----------------|---------|

| :2        | <u>File E</u> dit | <u>V</u> iew <u>I</u> r | nsert F <u>o</u> rma | at <u>T</u> ools | <u>D</u> ata <u>W</u> ind | ow <u>H</u> elp      |                       | -              | ₽×      |

| :         | 🙄 Arial           |                         | <del>•</del> 10      | • B I            | <u>n</u>   🖹 🗄            |                      | •                     | 💩 • <u>A</u> • | ;,<br>₹ |

| 1         | 1112              | 🔁 🖄                     | 1331                 | 2 🗄 😥            | 🛯 🕶 Reply w               | ith <u>C</u> hanges. | . E <u>n</u> d Review | A              |         |

|           | G13               | •                       | f <sub>x</sub>       | _                |                           |                      |                       |                |         |

|           | A                 | В                       | С                    | D                | E                         | F                    | G                     | Н              |         |

| 1         | Receiver          |                         |                      |                  |                           |                      |                       |                |         |

| 2         |                   |                         | ECU A                | ECU B            | ECU C                     | ECU D                | ECU E                 | ECU F          |         |

| 3         |                   | ECU A                   | -3.4E-09             | -3.3E-09         | 2.8E-09                   | 5.35E-09             | 1.57E-09              | 3.48E-09       |         |

| 4         |                   | ECU B                   | -6.3E-09             | 2.19E-10         | -2.3E-09                  | 4.17E-09             | -2.8E-10              | -7.6E-09       |         |

| 5         | Transmitter       | ECU C                   | -2.5E-09             | -2.7E-10         | 3.16E-10                  | -6.3E-10             | 9.75E-10              | -3.2E-09       |         |

| 6         |                   | ECU D                   | -4.1E-09             | 4.29E-09         | -2E-09                    | 7.53E-10             | -7.5E-10              | -4.4E-09       |         |

| 7         |                   | ECU E                   | 4.73E-10             | 1.46E-09         | -2E-09                    | 7.18E-10             | 4.79E-10              | 4.79E-10       |         |

| 8         |                   | ECU F                   | 3.84E-09             | -1.9E-09         | 1.75E-09                  | 6.41E-09             | 1.87E-09              | -4.5E-09       |         |

| Q<br> 4 4 | ► H\Shee          | t1 / Shee               | et2 / Sheet3         | /                |                           | •                    |                       |                | •       |

| Read      | ły                |                         |                      |                  |                           |                      |                       |                |         |

### Application Example Component Tolerances

- Only the nominal case was analyzed so far but...

- All components are associated with tolerances

- Impact of signal integrity can be significant

- Transceiver tolerances have significant impact on overall signal integrity

- Differential input voltage thresholds

- Detection of logical levels (correct signal decoding)

- Differential output voltage levels

- Signal propagation delays through transceiver

- May have a great impact in case of larger reflections

- Very important for the evaluation of the asymmetric delays

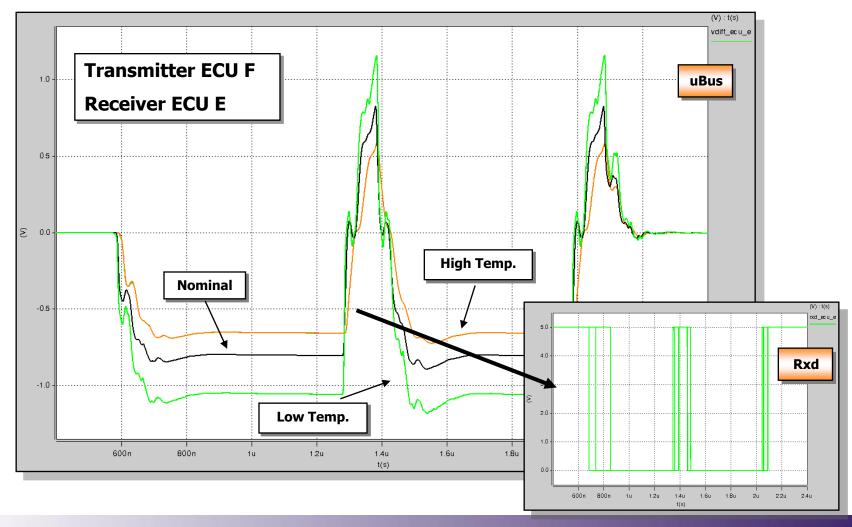

## Application Example Second Scenario – Nested Simulation

- Same Round Robin communication as before

- Same transmission rate as before

- Same bit pattern

- Transceiver tolerances

- Nested looped simulation runs

### **Application Example** Second Scenario - Signal Quality

### **Application Example** Second Scenario – Asymmetric Delays

- Tolerances impact asymmetric delays significantly

- Maximum value is now 22.5ns

- 3x larger compared to nominal case (-7.6ns)

- Considering RF reserve the topology is close to its limit (±30.75 ns)

| ×  | <u>File E</u> dit | ⊻iew Inser |          | <u>T</u> ools <u>D</u> at | - 11 <u>- 7</u> - 12 - 12 - 12 - 12 - 12 - 12 - 12 - 1 | Help              |           | - 6          |

|----|-------------------|------------|----------|---------------------------|--------------------------------------------------------|-------------------|-----------|--------------|

| -  | Arial             |            | • 10 •   | BIU                       |                                                        | ≡ 🔤 🛊             | !  🖽 🗕 🖄  | · <u>A</u> · |

|    | 12 22 (4)         | 9 bi 1     | 3313     | B () Y                    | Reply with                                             | <u>C</u> hanges E | nd Review | Ŧ            |

|    | G12               | • fs       | i.       |                           |                                                        |                   |           |              |

|    | A                 | В          | C        | D                         | Е                                                      | F                 | G         | Н            |

| 1  |                   |            |          | 1                         | Receiver                                               |                   |           |              |

| 2  |                   |            | ECU A    | ECU B                     | ECU C                                                  | ECU D             | ECU E     | ECU F        |

| 3  |                   | ECU A      | -2.1E-08 | -9.7E-09                  | 2.25E-08                                               | 1.29E-08          | 1.07E-08  | 1.38E-08     |

| 4  |                   | ECU B      | -1.7E-08 | 9.07E-09                  | -1.4E-08                                               | 1.26E-08          | -1.2E-08  | -1.8E-08     |

| 5  | Transmitter       | ECU C      | -1.2E-08 | -9.61E-09                 | 9.01E-09                                               | -8.9E-09          | 9.59E-09  | -1.3E-08     |

| 6  |                   | ECU D      | -1.5E-08 | 1.22E-08                  | -1.4E-08                                               | 9.27E-09          | -1.2E-08  | -1.5E-08     |

| 7  |                   | ECU E      | -1.2E-08 | 9.95E-09                  | -1.4E-08                                               | 9.18E-09          | 9.04E-09  | 9.04E-09     |

| 8  |                   | ECU F      | 1.42E-08 | -9.1E-09                  | 2.24E-08                                               | 1.43E-08          |           | -1.8E-08     |

| 9  |                   |            |          |                           |                                                        |                   |           |              |

| 10 |                   | N 10       |          |                           |                                                        |                   |           |              |

### **Application Example** Third Scenario - Ferrites as Filter

### **Application Example** Third Scenario - Signal Quality

SYNOPSYS\* Predictable Success

## Summary

- Verification of concepts in the early stage of the design process before real network is available

- Improved quality of network topology against possible issues

- System simulation allows to reduce development time through a partially automated evaluation process

- Deep system understanding

# Thank you for your attention!